描述

1.概述

選擇合適的電容器技術、存儲電感、開關頻率和半導體——相較其它因素——對于提高具有相對較高輸入和輸出電流的DC/DC開關電源的效率至關重要。一個高效的開關電源以及使用它的終端產品需要符合所有必要的EMC標準方可上市。這通常意味著輸入和輸出端必須另外加裝合適的濾波器,以降低干擾發生。然而,如果輸入和輸出電流較高,則很難在濾波器的效率、尺寸、阻尼、成本以及實際性能水平之間作出權衡。本文檔將通過一個100W升降壓DC/DC設計示例,簡要介紹作出這種權衡所需的注意事項、布局和器件。

圖 1:100 W 降壓-升壓轉換器的演示電路板。

2.項目范圍

設計一款滿足以下要求的升降壓轉換器:

18 Vout / Vin 14-24 Vdc 時 Pout 最高為 100 W

Iin max. = 7 A Iout max. = 5.55 A

輸出100W 時效率超過95%

符合CISPR32 Class B干擾限值(傳導和輻射)

低輸出紋波(低于 20mVpp)

無法屏蔽

長輸入和輸出線纜(各1m)

盡可能緊湊

性價比盡可能高

為了滿足這些嚴格的要求,必須設計出一種電感非常低、緊湊布局,以及能夠匹配轉換器的濾波器。如果考慮EMC,輸入和輸出線纜是頻率范圍高達1GHz的主要天線。由于現代四開關升降壓轉換器在輸入和輸出端都具有高頻電流環路,因此必須根據工作模式對輸入和輸出進行濾波。這可以防止由于MOSFET快速開關導致的高頻干擾進入線纜并產生輻射。

圖2:高頻 ΔI/Δt 環路和臨界ΔU/Δt開關節點電路圖,具體取決于轉換器工作模式。

本應用使用了來自Linear Technology (Analog Devices) 的開關穩壓器LT3790。其輸入電壓范圍高達60VDC,開關頻率可調,可控制四個外部MOSFET,使設計具有高度靈活性。

3.設計和測量

升降壓電路設計的主要特點:

雙面6層印刷電路板

400kHz開關頻率

扼流圈中的電流紋波約為額定電流的30%

緊湊型60V MOSFET,具有較低的Rdson、Rth和封裝ESL

1Ω柵極串聯電阻

圖3:轉換器功率級簡圖。

3.1.電感選擇

利用REDEXPERT在線平臺,可以快速、輕松、精確地選擇合適的電感。在此案例中,必須先為降壓操作輸入一次操作參數(Vin、fsw、Iout、Vout、ΔI),再為升壓操作輸入一次。

在降壓操作中,需求一個更大的電感以及一個更小的最大峰值電流 (7.52 µH/5.83 A)。

在升壓操作中,電感減小了,但最大峰值電流會增大 (4.09 µH/7.04 A)。

使用REDEXPERT選擇電感的另一個好處是:可以根據不同器件復雜的交流和直流損耗、產生的器件發熱以及它們的明顯參數(尺寸、額定電流等),對它們進行比較。

在此案例中,選擇了WE-XHMI系列屏蔽電感,電感值為6.8μH,額定電流為15A。由于采用現代制造技術,該器件的RDC極低,尺寸極小,僅15x15x10mm(長/寬/高)。其創新的磁芯配比材料還使其具有不受溫度影響的軟飽和特性。

圖 5:WE-XHMI 74439370068 的 REDEXPERT 仿真(降壓操作)。

3.2.輸入電容器選擇

由于流過濾波電容器的脈沖電流較高,并且要確保較低的輸出紋波,因此鋁聚合物和陶瓷電容器的組合成為最佳選擇。一旦最大輸入和輸出電壓紋波設置完成后,可使用以下公式計算所需電容。

選擇的電容:6 x 4.7µF / 50V / X7R = 28.2 µF (WCAP-CSGP 885012209048)

使用REDEXPERT,可以輕松、快速地確定MLCC的直流偏置,得出的值更接近實際,參見圖6。結果:必須考慮到輸入電壓為24V 時電容會減少20%;因此有效容值只有23μF,但已足夠。此外,將一個 68μF/35V WCAP-PSLC鋁聚合物電容器與陶瓷電容器并聯使用,串聯一個0.22Ω SMD電阻。這有助于轉換器的負輸入阻抗與輸入濾波器保持穩定(更多信息請參見ANP044)。由于該電容器也會有一定量的高脈沖電流流過,因此鋁電解電容器在此案例中不太適用。較高的ESR會導致該類電容器溫度過高。

圖6:所選MLCC的REDEXPERT阻抗、ESR和直流偏置圖。

3.3.輸出電容器選擇

選擇的電容:6 x 4.7 µF / 50 V / X7R = 28.2 µF – 15% 直流偏置 = 24 µF (WCAP-CSGP 885012209048)

另加:1個鋁聚合物電容器以快速響應瞬態信號:

WCAP-PSLC 220µF/25V

圖7:100W升降壓轉換器電路圖(包括所有濾波器器件)。

3.4.PCB 頂層布局分析

圖8:降壓-升壓轉換器的 EMC 優化頂層布局(省略輸入和輸出濾波器組)。

1.陶瓷濾波電容器布置緊密,使得高 △l/△t 的輸入和輸出環路結構非常緊湊。

2.電路中的敏感的、高阻抗的模擬部分的 AGND 覆銅表面分離且順滑(僅 PIN30 連接到 PGND)。

3.非常靠近開關電源IC的緊湊型自舉電路。

4.并聯電容的電流測量連接按差分線路布線,采用干凈的開爾文連接。

5.通過寬帶 π型 濾波器對開關穩壓器 IC 的內部電源做去耦濾波

6.為了達到電路板底部和內部PGND層的低電感和低阻抗需使用盡量多的過孔。

7.大面積覆銅可以作為良好的散熱片并提供低 RDC,但不得超過必要的面積,特別是在兩個“熱”△U/△t 開關節點上,以免形成不必要的天線。

3.5.PCB 底層布局分析

圖 9:降壓-升壓轉換器的EMC優化底層布局,包括四個功率MOSFET、剩余的濾波電容器、并聯電容和續流二極管。

8.在靠近FET的位置布置陶瓷濾波電容器,使得高△l/△t的輸入和輸出環路結構非常緊湊。

9.幾何形狀布局和覆銅表面的使用意味著FET之間以及FET與并聯電容之間的連接的阻抗和電感極低。

10.具反向幾何形狀的電容分流器,可進一步降低寄生電感;因此,HF電流環路也可減至最小。

11.由于沒有其它大型器件阻礙熱傳導,因此PCB底面上的半導體可以得到更好的冷卻。

12.超快恢復肖特基二極管緊鄰相應的 開關FET布置。

13.大面積覆銅可以作為良好的散熱片并提供低RDC,但不得超過必要的面積,特別是在兩個“熱”△U/△t開關節點上,以免形成不必要的天線。

3.6.中間層布局分析

圖 10:中間層3的布局。

圖 11:中間層2、4、5的布局。

所有四個中間層基本都為PGND覆銅表面,因此具備相應的優點:

熱損失分布均勻。

電流饋電和返回路徑始終形成盡可能小的環路面積,從而最大限度減少關鍵EMC環路天線。

一定量的關鍵EMC高頻噪聲HF 在PGND表面轉換為熱量(渦流效應)并因此被吸收。這種效應會隨著PGND和HF相關部件之間的距離減小而增加。

部分屏蔽。

MOSFET柵極的引線在兩個PGND層內布線,因此可完全屏蔽。

具有GND電位的過孔圍繞PGND邊緣以規則的間隔布置。這些可以抵消潛在的邊緣輻射。

3.7.輸入和輸出濾波器器件

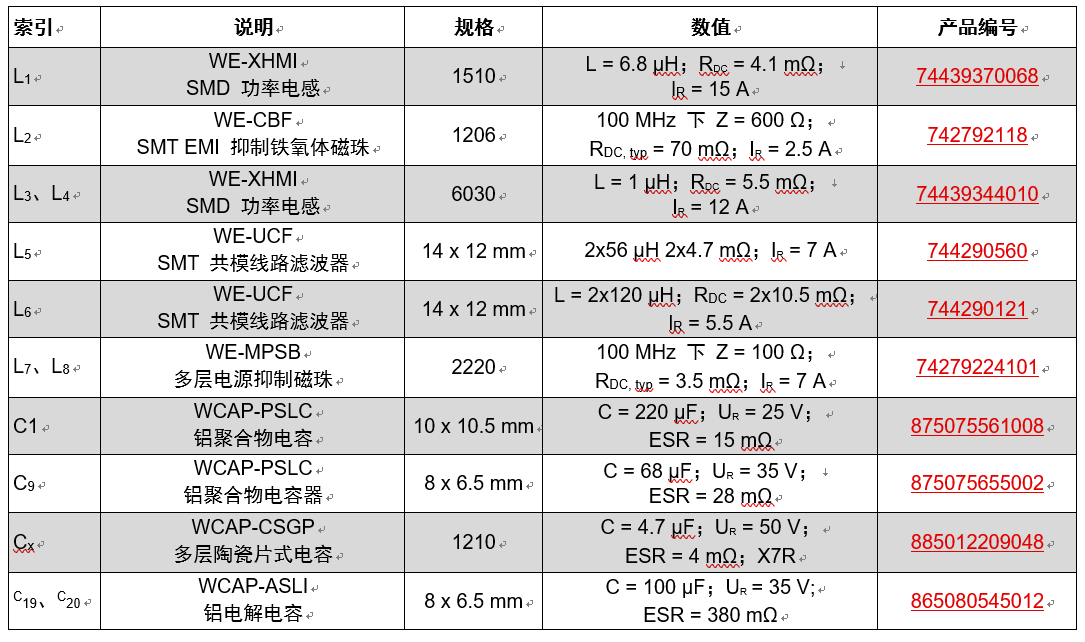

選擇濾波器器件時,必須能夠達到150kHz – 300MHz 的寬帶干擾抑制。這應足以抑制預期的傳導和輻射EMC干擾。但如果輸入或輸出處使用的線纜被縮短或省略了,則濾波器也可被簡化。

3.8.不含濾波器的EMC測量 (100W Pout)

為滿足大多數應用的需要,轉換器的干擾不得超出Class B (家用)限值,包括傳導 (150kHz – 30MHz) 和輻射 (30MHz – 1GHz) 范圍,參見圖12 和13。

鑒于此處需要的電流,除了插入損耗非常重要之外,電感元件還必須具有盡可能低的RDC,從而將效率和自熱保持在一個可接受的水平。遺憾的是,低RDC通常意味著需要增大設計尺寸。因此,使用最先進的元器件在這里也尤為重要,它們可以在RDC、阻抗和尺寸之間達到完美的平衡。WE-MPSB系列以及WE-XHMI系列的緊湊設計特別適合于此案例。廉價的鋁電解電容器(如 WCAP-ASLI)適合作為電容值為10μF以上的濾波器的電容器件。與上面提到的刻薄電容器不同,此處不會出現高紋波電流(濾波器電感會有效阻止這些電流),因此它們不需要承受高紋波電流。因此,較高的ESR也不是問題,這甚至還有助于保持低的濾波器系數,從而防止其它不必要的振蕩。

圖12:不含輸入濾波器時的傳導干擾測量。果然,盡管布局良好,但干擾超出了B類限值。

圖13:不含輸入和輸出濾波器時的輻射干擾測量。在大約180MHz 下,干擾和限值之間的差異非常小,這可能會導致后續測量出現問題。其原因是肖特基恢復電流的快速反向恢復時間刺激了寄生 LC 諧振。

圖15 顯示了輸入和輸出濾波器的結構(共模和差模)。圖16 顯示了該濾波器在EMC相關頻率范圍內對差模插入阻尼的仿真。

圖14:三種不同頻率范圍的濾波器元件框圖。

圖15:輸入和輸出濾波器組差模插入阻尼的LTSpice仿真(僅漏感與CMC相關)。

圖16:仿真差模插入衰減與兩個濾波器組的寄生特性。最高 500MHz 下,可實現超過80dB的插入損耗。

其它的濾波器損耗由電感器中的歐姆損耗導致:

輸出濾波器損耗:I2 • Rdc = 5.5 A2 • 30 mΩ = 907 mW

輸入濾波器損耗:|2 • Rdc = 7 A2 • 18.4 mΩ = 902 mW

共模電感的選擇標準如下:

在較寬的頻率范圍內(此案例為150kHz至300MHz)盡可能達到最大共模阻抗。

分段繞組技術,以獲盡可能大的漏感(差模干擾抑制)。

低RDC。

緊湊型設計和SMT。

3.9.具輸入和輸出濾波器的PCB上表面布局分析

1.布置兩個濾波器組時,盡可能消除與電路主要部分的電感和電容耦合;否則可能會影響濾波效果。

2.內層中的PGND覆銅表面僅與濾波器的兩個鋁電解電容器連接。濾波器組下沒有覆銅,即便中間層也是如此。這可以避免電流耦合,否則會降低濾波電容器的抑制效果。

圖17:使用的兩個WE-UCF共模電感的共模和差模阻抗曲線

3.設計T型濾波器時,盡可能消除三個器件內不必要的電容和電感耦合。

4.兩個共模電感下方沒有覆銅,以便最大限度減少電容耦合

圖18:頂層視圖,包括符合CISPR32 B類的所有濾波器元件

圖 19:頂層測量

3.10. 100 W Pout (Ta = 22 °C)下濾波器的溫度和效率測量

100 W Pout 下的效率測量結果:

降壓模式 96.5 %

升壓模式 95.6 %

元器件的最高溫度低于64°C,這為更高的環境溫度提供了足夠的余量,同時器件上受到的壓力也比較低。同樣效率也非常高,特別是考慮到這會影響所有過濾器器件。

圖20:底層測量

4.總結

盡管具有精細的布局以及合適的有源和無源器件,但此案例中苛刻的規格要求(如長電纜、缺少屏蔽等)意味著如果不額外加裝濾波器,就無法符合Class B標準。但是,由于這一問題在意料之中,可以從一開始就設計合適的濾波器。因此,本文檔設計了一款靈活、高效且符合B類標準的100W降壓-升壓轉換器。為使電路板更加緊湊,可將兩個濾波器組旋轉90°或布置在PCB底面。借助如REDEXPERT和LTSpice等設計和仿真軟件,可以快速、低成本地得出結果。

圖21:含上述輸入濾波器時的傳導干擾。在整個測量范圍內,平均和準峰值干擾均未超出規定限值。

圖22:含上述輸入和輸出濾波器時的輻射干擾。在整個測量范圍內,干擾均未超出規定限值(水平和垂直)。

A. 附錄

A.1. 物料清單

|